module srflipflop(q,qbar,s,r,clk);

input s,r,clk;

output reg q,qbar;

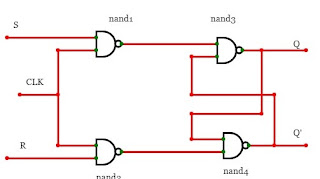

wire x,y;

nand g1(x, s,clk);

nand g2(y,r,clk);

nand g3(q, qbar,x);

nand g4(qbar,q,y);

endmodule

Behavioral Level Modelling

module srflipflop(q,qbar,s,r,clk);

input s,r,clk;

output reg q,qbar;

always@(posedge clk)

begin

case({s,r})

2'b00: begin q<=q; end

2'b01: begin q<=0; end

2'b10: begin q<=1; end

2'b11: begin q<=z; end

endcase

end

endmodule

No comments:

Post a Comment